Increasing on-chip network efficiency for improving the performance of chip multiprocessors supporting simultaneous parallel applications

Funded by Junta de Comunidades de Castilla-La Mancha. PEII-2014-028-P and European Commission (FEDER funds) (2014-2017).

Current semiconductor manufacturing techniques allow to include multiple cores on the same chip. This has been used by the microprocessor industry to keep increasing the computing speed, favouring multicore chips instead of an increasingly powerful uniprocessor. Power consumption, heat dissipation, or cost are some of the main concerns against the latter, motivating that decision. Although these cores do not necessarily run as fast as the highest performing single-core processors, they all together improve the overall performance. Therefore, chips containing tens or even hundreds of identical cores are expected in the future. Chip Multiprocessors (CMPs) are an excellent example of these systems.

To take full advantage of CMPs, it is also expected that several applications will run simultaneously on such CMP systems. Moreover, as the

number of cores is likely to increase, it is expected that the number of applications to run in the same CMP will also increase. In this scenario,

all resources in the CMP are shared by the applications. If resource allocation is not managed in an efficient way, performance of any individual

application can be seriously affected. All CMP components have an important role in the CMP performance. Cores, caches, memory controllers, and the

interconnection network must be carefully designed to contribute to applications reaching their required performance levels.

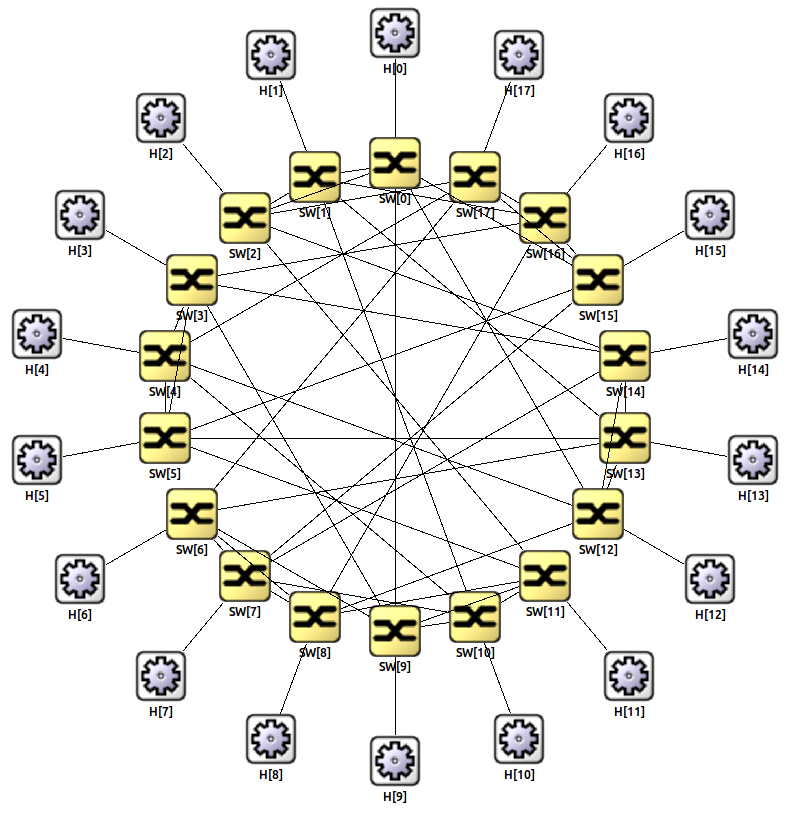

This project focuses on the interconnection network (network-on-chip or simply NoC, in the CMP context). Since current and future applications running on

CMPs can be of diverse nature (e.g. computer vision, media processing, animation, simulations, data

mining, etc.), the global traffic pattern can be completely unpredictable because of the different program behaviors for different

external inputs. Consequently, it is much more difficult to manage network traffic if several applications coexist in the same CMP. In this scenario,

the network traffic interferences between applications increase and the performance of individual applications can suffer an important degradation.

On the other hand, due to the increasing number of cores, congestion situations will be more likely to happen in future CMP systems. As these

situations may lead to a severe network performance degradation, it would be interesting to have efficient congestion management techniques oriented to

keep CMP performance even in congestion situations.

New techniques will be proposed with the aim of improving network global performance, thereby also improving the

performance of individual applications when they simultaneously run in the CMP. Resource virtualization, quality of service and congestion management

techniques, considering electrical and photonic technologies, are explored to achieve such objective.